自2017年士兰微电子推出首颗DIP25封装的IPM模块,至今已有上千万颗模块用在千家万户。它可能出现在你家的洗衣机里,为你不辞辛苦地褪去污浊;它可能出现在你家的冰箱里,为食品的保鲜保驾护航;它还可能出现在你家的空调里,为你送来冬暖夏凉……

本文将带你走近DIP25系列IPM,探讨它强有力的心脏IGBT,了解它的短路测试方法、短路能力以及过流保护设置,也便于让各位工程师朋友在应用中更得心应手。

1.短路测试

对于电机控制系统中,一个关键要求就是在负载短路时能安全关断:当负载短路,集电极的电流迅速上升至极限输出,器件能在此条件下安全关断,系统能够得到可靠保护;同时从另一方面说,短路时IGBT承受的电压和电流应力在短路持续期间产生的能量是非常巨大的,因此可以把短路视为系统最恶劣的情况之一。

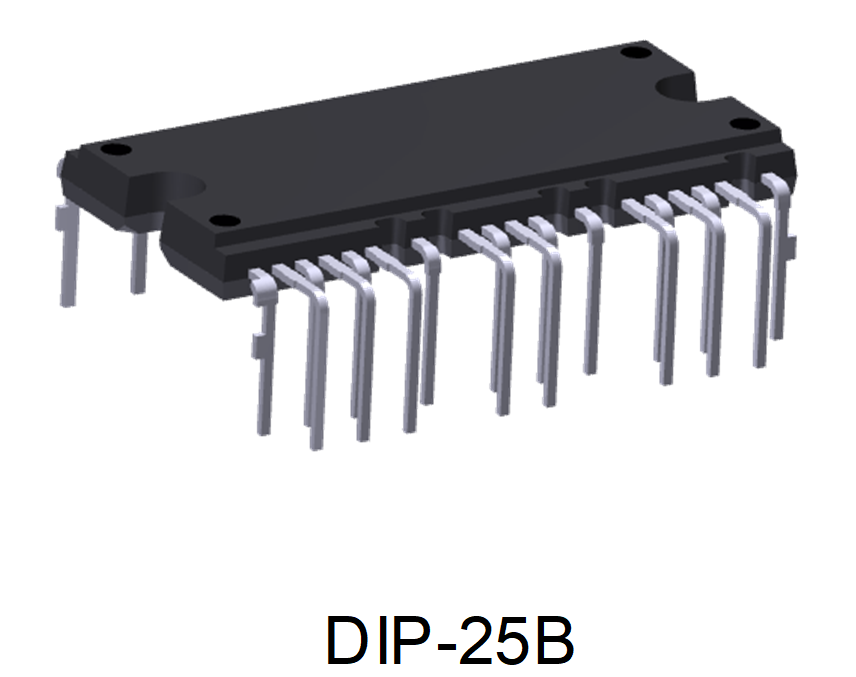

下图所示,给出了士兰DIP25系列IPM短路电流及能力测试的原理图,具体测试方法如下:

图1 短路测试电路图

以W相高侧为例:

DIP25模块CSC接地,使能/SDW上拉5.1k至5V,VCC接15V,INWL接地或者悬空均可,VPN接400V高压源,W相低侧IGBT短路即W与NW用粗短线短路;

INWH接信号发生器,单脉冲输出,幅值5V,脉宽设置为2us;

示波器电流探头接IC,高压探头接P与W端口,普通探头接INWH与COM,调节好量程,设置INWH信号上升沿触发;

信号发生器触发输出,即可得到模块W相高侧短路电流波形;

继续增大INWH脉宽直至IGBT损坏,即可得到W相高侧IGBT的短路能力。

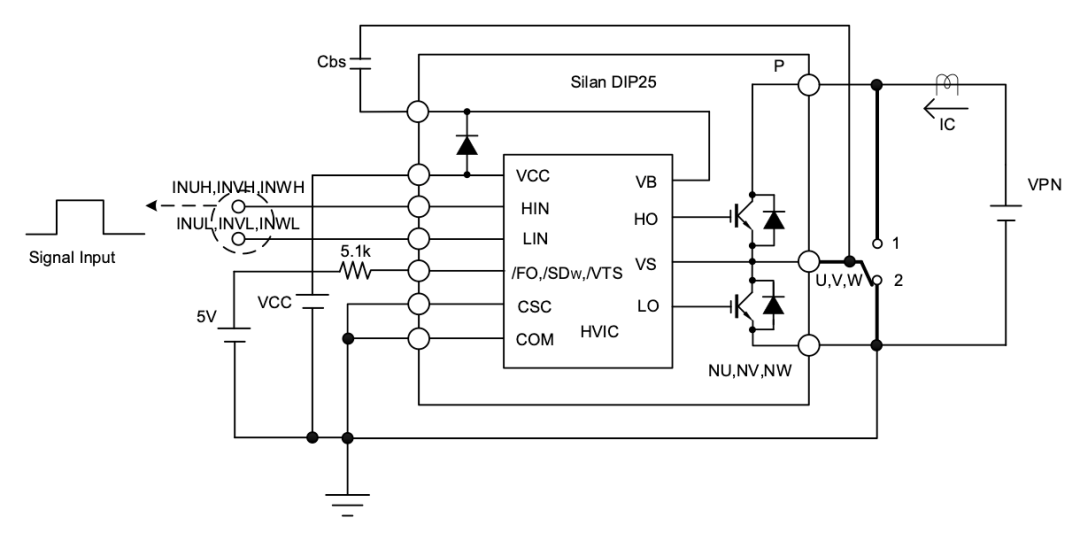

Tc=125℃,VPN=400V,VCC=16.5V,实测波形如下:可以承受6uS。

图2 短路测试实测波形

注意事项:

1)需注意测试平台高压侧走线长度和宽度,注意粗短路线长度,因为会影响短路回路杂散电感和线路阻抗,进而影响短路电流测试值,同时也会影响电路关断时的电压尖峰大小;

2)测试高侧时,由VCC经自举二极管供电,实际测试时可适当增加电压弥补二极管压降;

3)Csc短路是为了屏蔽IPM模块的过流保护,测试U和V相时,Csc无需接地;

4)上高压前需调试好弱电信号,信号输出与预设时间一致,信号发生器应调至触发输出模式,以免上电导致模块损坏;

5)示波器同时抓取VIN, VCE, ICE波形;

6)PN电压可先加50V确认波形是否正常后再加至400V;

7)拆装模块时,注意先给PN放电,以免人体接触后被电;

8)短路能力测试IPM模块可能会过热炸裂,注意遮挡;

9)确认测试的环境和模块温度在IPM模块规格书要求范围之内;

10)短路电流下降为结温升高导致。

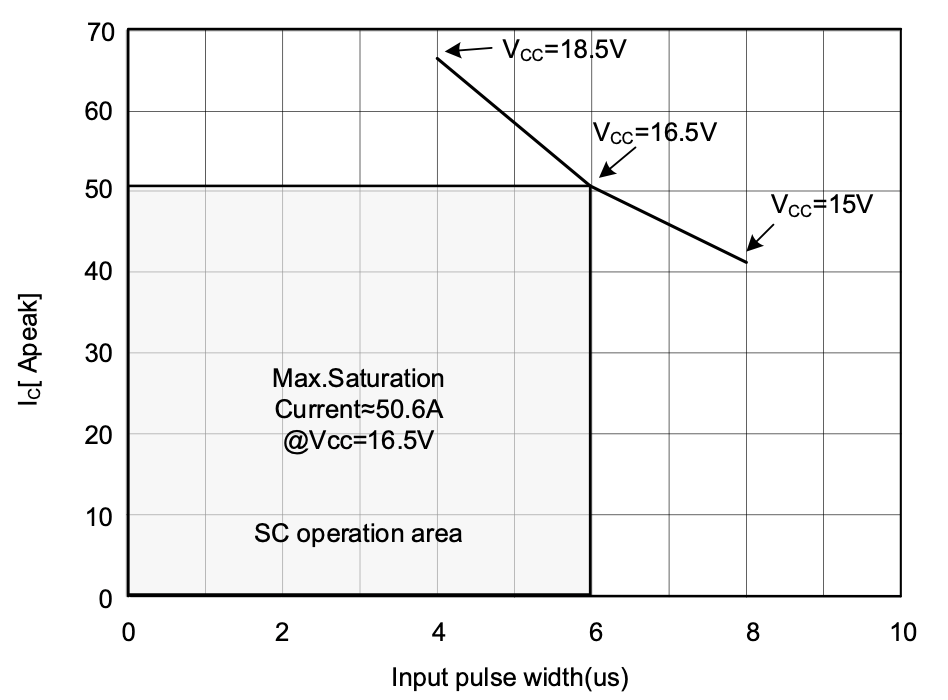

经测试,得到SDM06C60TA2的SCSOA曲线如下:Tc=125℃,VPN=400V。

曲线下面灰色阴影区为安全工作区。

图3 SDM06C60TA2 SCSOA曲线

2.过流保护设计建议

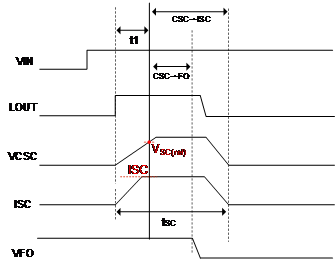

DIP25系列IPM过流保护时序大致如下:发生短路,电流上升,CSC电压上升,t1为CSC的RC滤波时间,检测到过流点阈值后,经过一段延时VFO端口拉低,降低至IPM模块使能关断阈值后,LOUT输出低,低侧IGBT关断。

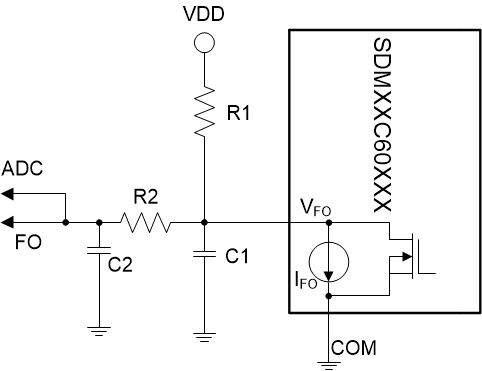

图4 过流简易时序 图5 VFO端口连接图

VFO端口外围连接如图5所示,为保证模块发生过流保护时的可靠性,考虑到IPM的安全工作区,这里需要对保护响应时间有所要求,即从发生过流到FO拉低的总时间要小于3us,该时间主要有2段组成:

1.CSC的RC延迟时间,小于1.5us;

2.VFO放电时间,小于1.5us。

条件1小于1.5us,通过RC参数设置,建议Ccsc为1nF,Rcsc为1.5KΩ;

这里重点考虑VFO的放电时间的设置,出现过流保护时,VFO开漏NMOS打开,VFO电压开始下降,有VFO滤波电容对NMOS放电,放电时间取决于滤波电容的大小(NMOS等效电阻为50Ω),当VFO电压低于1.3V(典型值)时,模块输出才会安全关断。

出现保护故障输出,内部NMOS导通,C1通过NMOS放电,此时该端口电压为(理想情况下,公式暂不考虑内部恒流源放电):

VFO=V0 +(V1-V0)× [1-e(-t/RC1)]——(公式1)

这里V0为出现保护前的VFO端口电压,V1为VFO端口能放电到的最低电压(通常取0.1V),VFO为t时刻电压(保护时刻取VFO为使能关断最小值0.8V),R为NMOS等效电阻取50Ω。代入公式1换算得到:

t=RC1 × ln[(V1 - V0)/(V1 -VFO)]=50Ω×C1 ×ln[(0.1 - V0)/(0.1– 0.8)]<1.5us

得到

C1<1.5/(50 ×ln[(0.1 - V0)/-0.7])——(公式2)

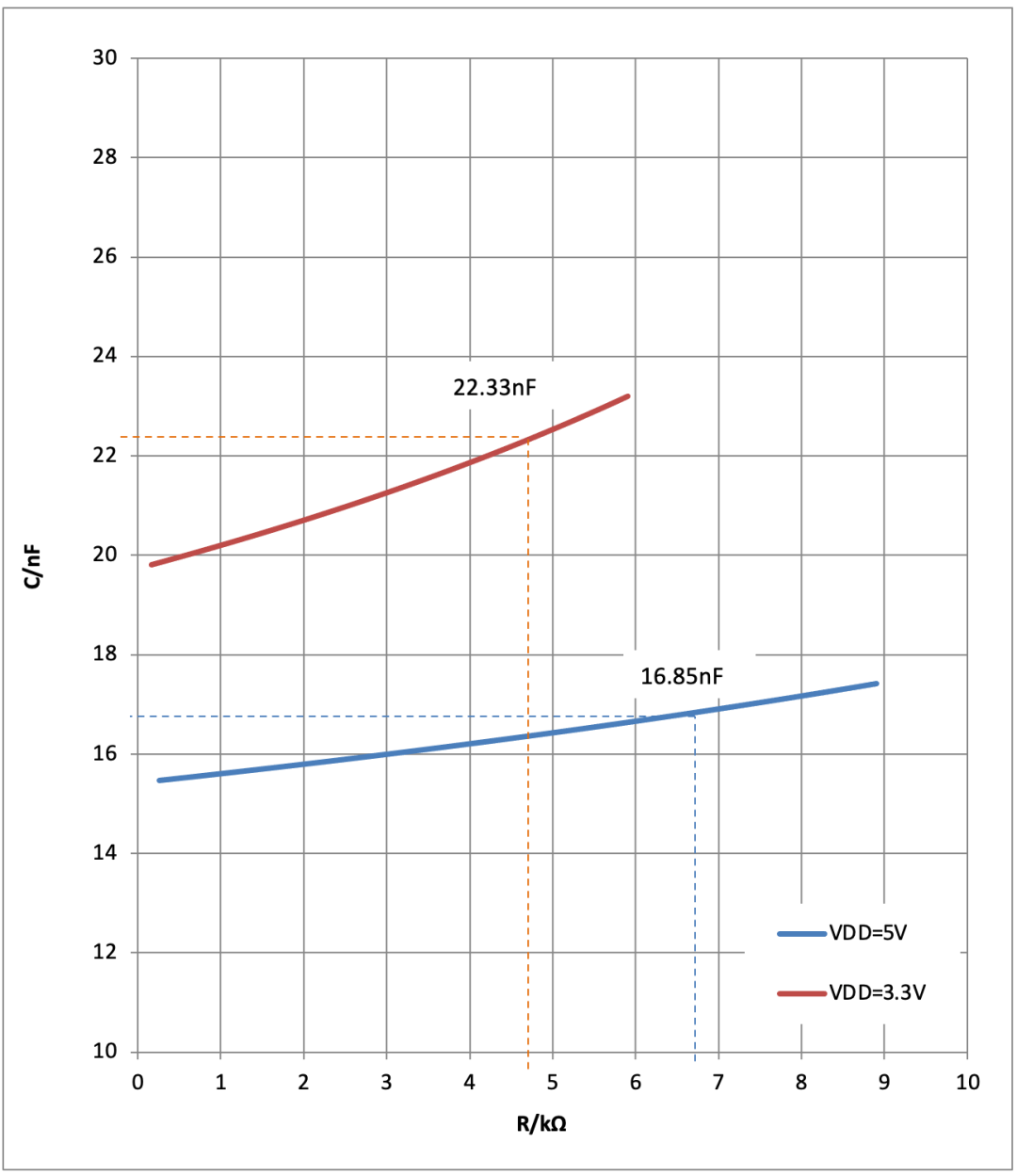

Tc=25℃下,VO与上拉电阻关系如下:

VO=VDD-0.11*R1——(公式3)

代入公式2,得到C1与上拉电阻R1的关系如下:

C1<1.5/(50 ×ln[(0.1 - (VDD-0.11*R1) )/-0.7]) ——(公式4)

例如:VDD=5V,上拉6.8K,温度25°C,则V0=4.25V,得到C1<16.85nF

图6 VFO滤波电容与上拉电阻关系

为保证短路保护的可靠性,留足够的余量,这里建议统一滤波电容取值为2nF。

注意事项:

1)为防止地线电压波动导致VFO容易被误触发使能关断模块输出,VFO管脚的滤波电容应尽可能靠近管脚放置;

2)尽量在MCU的AD管脚处也放置一个1nF电容,以免走线过长导致的电压波动;

3)根据整机应用实测情况,合理调整VFO滤波电容大小。